삼성전자, HBM4서 '역전' 노린다…로직다이 공정 고도화 추진

[지디넷코리아]

삼성전자가 차세대 HBM(고대역폭메모리) 시장을 주도하기 위한 새 공정 기술 적용에 나서 주목된다. 삼성전자는 최근 내부적으로 HBM4(6세대 HBM)의 필수 구성 요소인 '로직다이'에 보다 진보된 공정을 적용하기 위한 논의에 들어간 것으로 파악됐다.

27일 업계에 따르면 삼성전자는 HBM4의 로직다이를 당초 8나노미터(nm)에서 4나노 공정으로 설계하는 방안을 추진하고 있다.

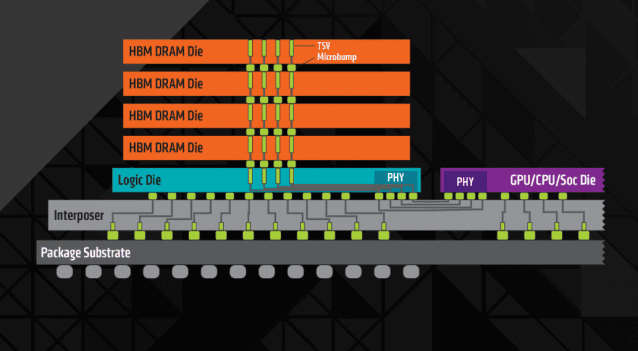

HBM은 TSV(실리콘관통전극)을 통해 여러 개의 D램을 수직으로 적층한 메모리다. 데이터 전송 통로인 I/O가 기존 D램 대비 수십 배로 증가해, 성능을 획기적으로 끌어올린 것이 특징이다.

현재 주요 메모리 업체들은 HBM을 4세대(HBM3)까지 상용화하는 데 성공했다. 5세대인 HBM3E는 내년부터 본격 양산된다.

나아가 6세대인 HBM4는 또 한번 기술적 변혁을 이뤄낼 전망이다. HBM4의 I/O 수는 2048개로, HBM3(1024개) 대비 2배 많다. 주요 업체들이 목표로 정한 HBM4의 양산 시점은 내후년인 2025년이다.

제조 공정에도 변화가 일어난다. 기존 HBM에는 D램과 D램 사이를 수천 개의 마이크로 범프(Bump)로 연결하는 패키징 기술이 쓰였다. 반면 HBM4부터는 하이브리드 본딩이 적용된다. 하이브리드 본딩은 마이크로 범프 대신 구리를 통해 칩을 직접 연결한다.

또한 기존 D램 공정에서 생산되던 로직다이가 파운드리에서 양산되는 구조로 바뀐다. 로직다이란 HBM을 적층한 코어다이의 메모리 컨트롤러 기능을 담당하는 다이다. HBM과 GPU 등 시스템반도체를 PHY(물리계층)으로 연결해 데이터를 고속으로 연결한다.

특히 삼성전자는 이 로직다이의 성능을 한층 강화하는 전략을 구상하고 있다. 당초 삼성전자 및 주요 경쟁사는 로직다이의 공정을 8나노로 설계해 왔다. 최근 삼성전자는 해당 설계를 4나노로 변경하는 방안을 추진 중인 것으로 파악됐다.

로직다이의 선폭을 줄이는 경우 HBM의 PPA(성능, 전력효율성, 면적)를 전반적으로 향상시킬 수 있다. 나아가 4나노 기반의 로직 기능을 추가할 수 있어, 고객사의 요구에 맞춰 맞춤형 제품을 공급하는 데 유리하다.

해당 사안에 정통한 관계자는 "삼성전자가 기술적으로 충분히 공정 전환이 가능하다는 판단 하에 해당 사안을 내부에서 적극 논의하고 있다"며 "단순히 성능 면이 아니라 고객사가 원하는 기능을 지원할 수 있다는 점에서 매력도가 높은 아이디어"라고 전했다.

또 다른 관계자는 "삼성전자가 메모리만이 아니라 파운드리, 시스템LSI를 동시에 개발한다는 점에서 로직다이의 감정을 부각시킬 수 있다"며 "다만 HBM4의 양산 일정이 미뤄질 수도 있다는 점은 변수"라고 말했다.