4나노 수율 높인 삼성전자, 잇단 수주...TSMC와 경쟁서 유리

[지디넷코리아]

삼성전자가 4나노미터 공정 수율을 TSMC 수준으로 높이면서 파운드리 시장에서 고객사 확보에 유리해졌다는 평가가 나온다. 삼성전자는 올해 4나노 공정에서 신규 수주에 연이어 성공하면서 가시적인 성과를 내고 있다.

16일 시장조사업체 트렌드포스는 4나노 공정 수율은 삼성전자 75%, TSMC 80%로 추정된다고 밝혔다.

삼성전자가 2021년 첫 4나노 공정으로 생산했을 당시 수율이 50%였다. 불과 2년 만에 25%P를 더 끌어올린 셈이다.

삼성전자는 4나노 수율이 높아지면서 가격 경쟁력 면에서 우위에 설 수 있게 됐다. 통상 삼성전자의 파운드리 가격은 같은 공정에서 TSMC 보다 저렴하다. 고객 입장에서는 수율이 비슷하다면 가격 부담이 적은 삼성전자를 더 선호할 수 있다는 의미다.

IT 업계 유명 소식통인 레베그너스(Revegnus)는 트위터에서 애플 고위급 회의에서 얻은 정보를 공개하면서 "TSMC 3나노 수율은 63%지만, 4나노 공정 보다 2배 비싸다"고 전했다.

트렌드포스는 "삼성의 수율과 생산 능력이 크게 향상되고, TSMC의 가격 인상 결정으로 인해 대형 고객사는 비용 및 지정학 등을 고려해 2차 공급업체를 찾아 아웃소싱 주문을 다양화할 수 있다"고 전망했다.

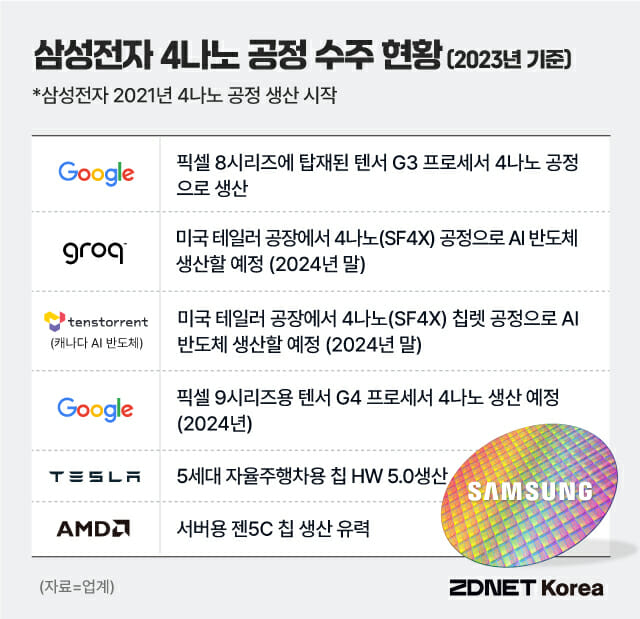

업계에 따르면 AMD는 내년 출시를 앞둔 코드명 프로메테우스(Prometheus) 젠(Zen)5C 서버용 칩을 삼성전자 파운드리 4나노 공정에 맡기는 문제를 놓고 최종 협상 중인 것으로 알려졌다. 일각에서는 AMD가 일부 물량은 TSMC 3나노, 삼성전자 4나노 공정을 동시에 활용할 수 있다는 관측도 나온다.

구글도 올해 스마트폰 픽셀 8시리즈에 탑재된 텐서 G3 프로세서를 삼성전자 4나노 공정에서 생산한데 이어 내년에 출시하는 픽셀 9시리즈용 텐서 G4 칩도 삼성전자 4나노 공정에서 생산하기로 결정했다.

또 테슬라는 5세대 자율주행차 칩 HW5.0을 삼성전자 4나노 공정으로 선택했다. 당초 테슬라는 해당 칩 생산을 TSMC에 맡기려고 했으나, 삼성전자의 수율 개선으로 결정을 바꾼 것으로 전해진다.

지난 8월에는 미국 AI 반도체 스타트업 그로크가 차세대 칩을 삼성전자가 현재 짓고 있는 테일러 공장에서 4나노 공정으로 생산한다는 계획을 발표했다. 지난 10월에는 캐나다 AI 반도체 기업 텐스토렌트가 삼성전자 테일러 공장에서 4나노 (SF4X) 칩렛 공정으로 칩을 생산한다고 공식적으로 밝혔다. 텐스토렌트는 AMD, 애플, 인텔, 테슬라 등에서 아키텍처 설계를 담당한 반도체의 전설 짐 켈러가 이끄는 기업이다. 짐 켈러 CEO는 이달 초 '삼성 AI 포럼' 강연을 위해 방한해 삼성전자 파운드리 협력에 대해 신뢰한다고 언급하기도 했다.

그로크와 텐스토렌트 칩이 생산되는 삼성전자 테일러 공장은 지난해 상반기 착공에 돌입해 현재 공사 중이며, 내년 말부터 4나노 공정으로 반도체를 양산할 예정이다.

이 외에도 삼성전자는 지난 7월 디자인하우스(DSP) 에이디테크놀로지와 함께 데이터센터에 공급되는 서버용 4나노 칩을 수주하기도 했다. 구체적으로 고객사를 밝히지는 않았지만 DSP 계약만 224억원 규모인 점을 감안하면, 고성능 칩 주문이 점쳐진다.

삼성전자는 첨단 공정에서 지속적으로 로드맵을 구축한다는 방침이다. 지난해 6월 첫 3나노 공정 양산에 이어 내년부터 3나노 2세대 공정을 시작한다. 또 2025년 모바일 향 중심으로 2나노 공정(SF2)을 양산하고, 2026년 고성능 컴퓨팅(HPC)향 공정, 2027년 오토모티브향 공정으로 확대한다. 2027년에는 1.4나노 공정을 양산한다는 목표다.